3A_chap2-system_architecture_overview

Contents

1. Overview Of the System-Level Architecture

每个段描述符都有关联的段选择器 , 后者提供 GDT 或者 LDT 内的一个索引 , 一个全局 / 局部标志 ( 指明段选择器指向 LDT 还是 GDT ) , 以及访问权限信息 , 因此段选择器的范围确定 GDT 和 LDT 包含的段描述符数 .

段描述符提供段的基地址 , 访问权限 , 类型和使用信息 .

访问段内的一个字节 , 不但需要段选择器确定段 , 还需要段内的偏移 .

TSS 定义了一个进程的执行环境状态 , 包括 : 通用寄存器 , 段寄存器 , EFLAGS 寄存器 , EIP 寄存器 , 三个带有段指针的堆栈段 ( 每个特权级有一个栈 ) 的段选择器的状态 . TSS 还包含与进程相关的 LDT 的段选择器和分页层次结构的基地址 .

当前进程的 TSS 的段选择器保存在进程寄存器 ( task register , TR ) , 切换到一个进程的最简单方式是调用或者挑战到新进程 —- 提供新进程的 TSS 的段选择器给 CALL 或 JMP 指令 .

IA32_EFER MSR 包含开启和操作 IA-32e 模式的相关域,还提供了和修改页访问权限相关的域 :

|

|

每个 bit 的说明如下 :

| Bit | Description |

|---|---|

| 0 | SYSCALL Enable : IA32_EFER.SCE ( R / W ) 在 64 位模式开启 SYSCALL / SYSRET 指令 |

| 7:1 | 保留 |

| 8 | IA-32e Mode Enable : IA32_EFER.LME ( R / W ) 开启 IA-32e 模式 |

| 9 | 保留 |

| 10 | IA-32e Mode Active : IA32_EFER.LMA ( R ) 设置表明 IA-32e 模式开启 |

| 11 | Execute Disable Bit Enable : IA32_EFER.NXE ( R / W ) 开启通过阻止执行从设置了 XD 位的 PAE 页中取回的指令进行的页面访问限制 |

| 63:12 | 保留 |

2. Memory-Management Registers

处理器提供了 4 个内存管理寄存器 ( GDTR , LDTR , IDTR , TR ) 指明控制分段内存管理的数据结构所在位置,用特殊的指令加载和保存这些寄存器 .

2.1. Global Descriptor Table Register

GDTR 保存基地址 ( 保护模式下 32 位 ; IA-32e 模式 64位 ) 和 16 位的 GDT 表大小限制 . 基地址是 GDT 字节 0 的线性地址 ; 表大小限制是表中的字节数 .

LGDT 和 SGDT 指令加载和保存 GDTR . 处理器上电或者重启后,基地址默认设置为 0 ,大小限制默认设置为 0FFFFH . 处理器初始化时必须加载一个新的基地址到 GDTR .

2.2. Local Descriptor Table Register

LDTR 保存 16 位段选择器、基地址 ( 保护模式下 32 位 ; IA-32e 模式 64 位 )、段限制和描述符属性 . 基地址是 LDT 段 0 字节的线性地址 ; 段限制是段中的字节数 .

LLDT 和 SLDT 指令加载和保存 LDTR 的段选择器部分 . 包含 LDT 的段必须在 GDT 中有一个段描述符 . LLDT 指令加载 LDTR 中的段选择器时,基地址、限制、描述符属性会自动加载到 LDTR .

进程切换时,自动加载新进程 LDT 中的段选择器和描述符到 LDTR , LDTR 的内容不会在写入新的 LDT 信息到寄存器之前自动保存 .

处理器上电或者重启后,段选择器和基地址设置为默认值 0 ,限制设置为 0FFFFH .

2.3. Interrupt Descriptor Table Register

IDTR 保存基地址和 16 位表限制 . 基地址是 IDT 字节 0 的线性地址 ; 表限制是表中的字节数 . LIDT 和 SIDT 指令加载和保存 IDTR . 处理器上电或者重启后,基地址设为默认值 0 ,限制设置为 0FFFFH . 基地址和限制在处理器初始化时设置 .

2.4. Task Register

TR 保存当前进程 TSS 的 16 位段选择器、基地址、段限制、描述符属性 . 选择器引用 GDT 中 TSS 描述符,基地址是 TSS 字节 0 的线性地址,段限制为 TSS 中的字节数 .

LTR 和 STR 指令加载和保存 TR 的段选择器部分 . LTR 指令加载段选择器到 TR 时,基地址、限制、描述符属性自动加载到 TR . 处理器上电或者重启后,基地址设置为默认值 0 ,限制设置为 0FFFFH .

切换进程时,自动加载新进程 TSS 的段选择器和描述符到 TR ,写入新的 TSS 信息到寄存器值前不会自动保存 TR 的内容 .

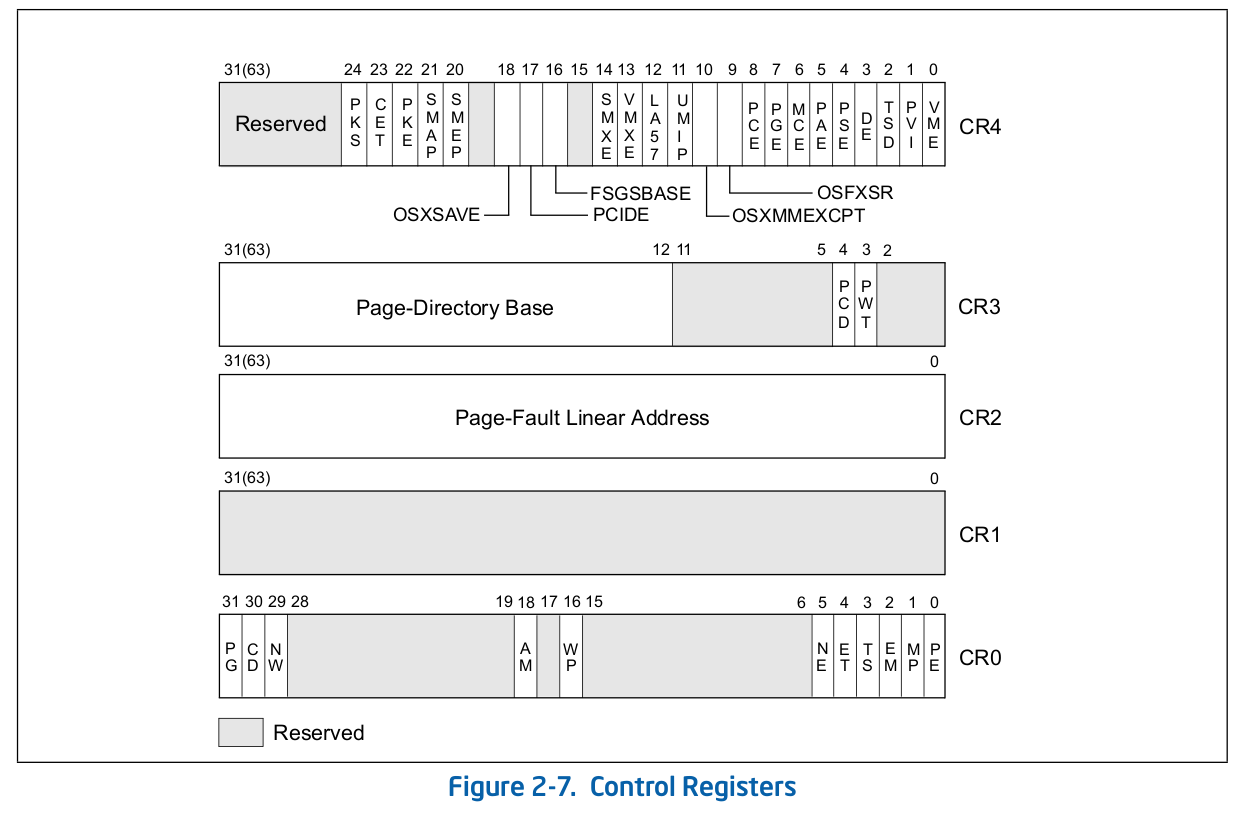

3. Control Registers

控制寄存器 ( CR0 , CR1 , CR2 , CR3 , CR4 ) 确定处理器的工作模式和当前正在执行进程的特性,这些寄存器在所有的 32 位和兼容模式下都是 32 位 .

64 位模式下,控制寄存器扩展为 64 位, MOV CRn 指令用于操作寄存器,这些指令的操作数大小前缀被忽略,存在下列事实 :

- 控制寄存器可以通过

MOV指令的 “move to/from cr” 形式读取或者加载 . 保护模式下MOV指令允许读取或加载 ( 只有特权级 0 ) 控制寄存器,这种限制意味着应用程序或者操作系统程序 ( 运行在特权级 1 2 3 ) 不能读取或者加载控制寄存器 . - CR0 和 CR4 的 bit 63:32 保留,必须写为 0 ,向高 32 位写入任何非零数都会导致一个 general-protection 异常 ( #GP(0) ) .

- CR2 的所有 64 位都可以由软件写 .

- 超出处理器物理寻址宽度的 CR3 bit 51:12 保留,必须为 0 .

MOV CR2指令不会检查写入 CR2 的地址是合法的 .- 64 位模式才有 CR8 寄存器 .

控制寄存器总结如下,每个寄存器的控制域单独介绍 .

-

CR0

控制操作模式和处理器状态 . -

CR1

保留 . -

CR2

包含缺页的线性地址 . -

CR3

包含分页层次结构的物理基地址和两个标志 ( PCD 和 PWT ) ,只指明了基地址的高位 ( 高于低 12 位 ) ,低 12 位假定为 0 . 因此第一个分页结构必须对齐到一个页 ( 4KB ) . PCD 和 PWT 标志控制处理器内部 cache 的分页结构 ( 不控制 TLB 中的页目录信息 ) .使用物理地址扩展时 ( PAE ) , CR3 寄存器包含页目录指针表的基地址 ; 4 级和 5 级分页, CR3 寄存器包含 PML4 表和 PML5 表的基地址 . 如果开启 PCID , CR3 和下图中的形式不同 .

-

CR4

包含的标志开启一些架构扩展,指明操作系统或者可执行文件对于特定处理器特性的支持 . -

CR8

提供对进程优先级寄存器 ( Task Priority Register , TPR ) 的读写,指明操作系统控制可以中断处理器的外部中断优先级阈值,只有 64 位模式可用,但是兼容模式下中断过滤仍然生效 .

几个控制寄存器中包含的控制位如下图所示 :

4. 总结

系统架构部分的寄存器可以分为以下几类 :

- 指明处理器的特性的寄存器,包括工作模式,浮点运算,保护机制等

- 内存管理相关的寄存器,分页,分段和进程切换,这些寄存器为了保证正确访问到执行指令所需的内存

- 中断和异常相关的寄存器

- 计数器,包括性能监视计数器和时间戳计数器

和通用的寄存器不同,系统架构相关的寄存器都有专用的指令进行读写,这些寄存器严重影响计算机系统的正常运转,因此一些指令需要较高的特权级才能执行 .

Author Globs Guo

LastMod 2020-10-10