3A_chap4-paging

Contents

1. Paging Modes and Control Bits

分页行为受 CR0 , CR4 , IA32_EFER MSR 和 EFLAGS 寄存器的影响 . 具体如何影响 , 以及怎样正确开启分页分页模式 , 需要按照一定的次序设置相关的寄存器 , 查阅 sdm .

不同分页模式相关寄存器的值和差异列出如下 :

| Paging Mode | CR0.PG | CR4.PAE | IA32_EFER.LME | CR4.LA57 | Lin-Addr Width | Phys-Addr Width | Page Sizes | Execute-Disable Support | PCIDs and Protection Keys Supports |

|---|---|---|---|---|---|---|---|---|---|

| None | 0 | N/A | N/A | N/A | 32 | 32 | N/A | No | No |

| 32-bit | 1 | 0 | 0 | N/A | 32 | Up to 40 | 4KB 4MB | No | No |

| PAE | 1 | 1 | 0 | N/A | 32 | Up to 52 | 4KB 2MB | Yes | No |

| 4-level | 1 | 1 | 1 | 0 | 48 | Up to 52 | 4KB 2MB 1GB | Yes | Yes |

| 5-level | 1 | 1 | 1 | 1 | 57 | Up to 52 | 4KB 2MB 1GB | Yes | Yes |

2. Access Rights

线性地址的转换过程完成后可以得到一个物理地址 , 转换的访问是否允许受访问权限的限制 .

线性地址的访问根据 CPL 分为用户模式或管理员模式的访问 : CPL = 3 是用户模式的访问 , CPL < 3 是管理员模式的访问 .

分页模式确定访问权限的方式和其访问模式密切相关 , 此外还受到分页结构项中的访问权限位 , CR0 , CR4 , IA32_EFER , EFLAGS 的影响 , 具体的判断方式查阅 sdm .

4 级和 5 级分页每个线性地址可以管理一个保护 key , 控制地址的数据访问 , 对于取指操作没有影响 .

3. Page-Fault Exceptions

访问线性地址可能产生缺页异常 , 原因可能是 :

- 访问的线性地址无法通过分页转化为物理地址 .

- 访问的线性地址可以转化 , 但是访问权限不允许 .

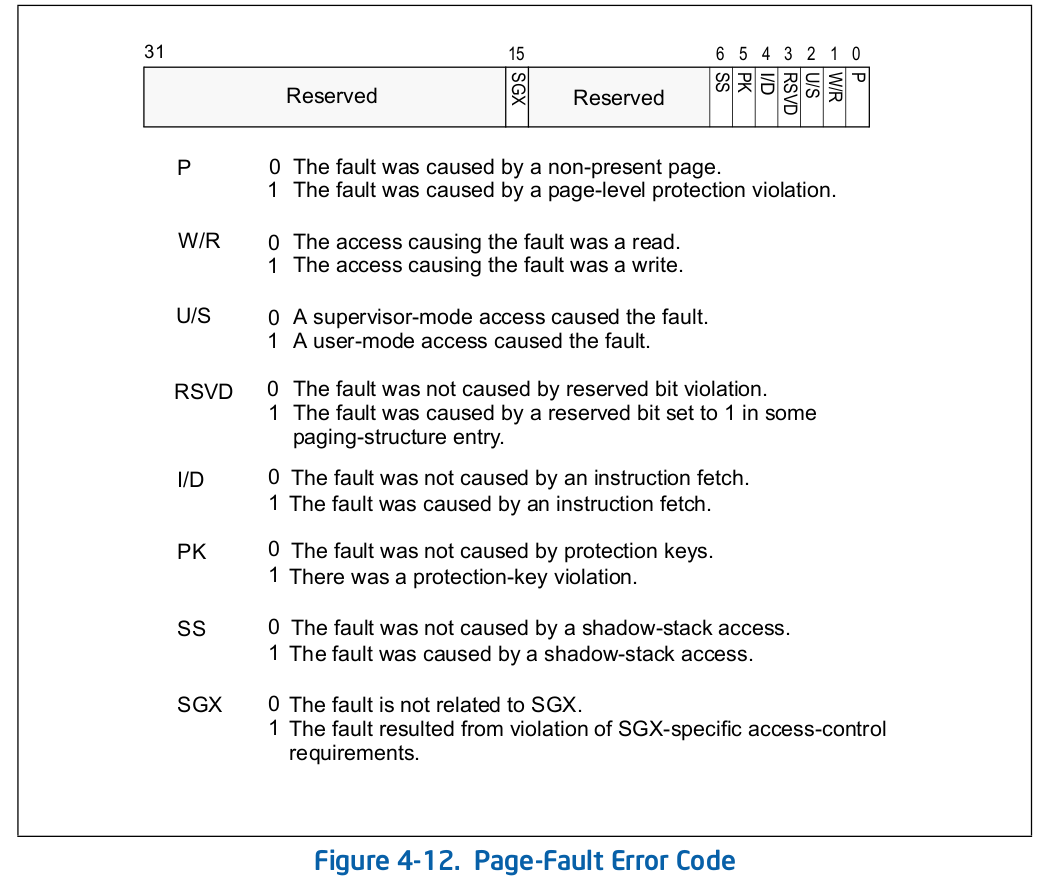

处理器通过缺页错误代码指明缺页产生的原因 :

4. Caching Translation Information

4.1. Process-Context Identifiers ( PCIDs )

PCID 是一个 12-bit 的标识符 , 供逻辑处理器缓存多个线性地址空间的信息 , 处理器可以在软件切换到使用不同 PCID 的不同线性地址空间时获取信息 .

逻辑处理器在 TLB 和分页高速缓存中创建项时 , 关联这些项到当前的 PCID ; 使用 TLB 和分页结构高速缓存中的项转化一个线性地址时 , 逻辑处理器只会用和当前 PCID 相关的项 .

4.2. Translation Lookaside Buffers ( TLBs )

TLB 包含虚拟页号到物理页号的映射 , 缓存线性地址的转化信息 .

TLB 中的每一项通过一个虚拟页号索引 , 包含线性地址转化过程中使用的分页结构项的以下信息 :

- 和虚拟页号对应的物理页号

- 转化线性地址使用的分页结构项的访问权限 :

- R / W 标志的逻辑与

- U / S 标志的逻辑与

- XD 标志的逻辑或

- 保护 key

- 标识最终页框的分页结构项中的属性 :

- 脏标志

- 内存类型

TLB 项可能包含其他信息 , 处理器可以实现多个 TLB , 根据用途包含不同的信息 , 比如只用于取指的 TLB 可能没有 R / W 标志信息 .

TLB 并不是处理器必须实现的组件 , 处理器也可以在任何时刻无效任何 TLB , 软件不能依赖 TLB .

TLB 只会缓存转化线性地址过程中用到的分页结构项 , 但是可能缓存由于分支预测或者投机执行产生的 , 实际执行程序时并不会发生的线性地址转化 .

CR4.PGE = 1 时 , 系统允许使用全局页 , 使用全局页的 TLB 项也是全局的 .

全局的 TLB 可以供所有 PCID 使用 .

4.3. Paging-Structure Caches

分页结构高速缓存是处理器在内存中缓存的分页结构信息 , 通过线性地址的一部分索引 , 保存的信息和 TLB 项类似 .

处理器可能为实际的代码路径中不会执行的 , 由于指令预取和投机执行的地址转化创建分页结构高速缓存 .

需要说明的是 , 分页结构高速缓存只包含引用其他分页结构 ( 没有映射页的结构 ) 的分页结构项中的信息 , 由于这些分页结构项没有使用 G 标志 , 全局页特性不会影响分页结构高速缓存的行为 .

4.4. Invalidation of TLBs and Paging-Structure Caches

处理器可能在线性地址转化时在 TLB 和分页结构高速缓存中创建项 , 并且在创建时使用的分页结构改变后仍然保有这些项 . 为了保证转化线性地址时使用修改过的分页结构 , 软件需要无效任何可能包含已经修改的信息的被缓存的项 .

下列指令可以无效 TLB 和分页结构高速缓存中的项 :

INVLPGINVPCIDMOV to CR0MOV to CR3MOV to CR4- 进程切换

- VMX 会话

此外 , 缺页也会无效 TLB 和分页结构高速缓存中的项 . 特别的 , 试图使用线性地址导致的缺页异常会无效关联到当前 PCID 所有和线性地址对应的虚拟页号的 TLB 项 ; 也会无效关联到当前 PCID 的所有该线性地址的分页结构高速缓存项 .

这些无效操作保证如果缺页异常不是由内存中的分页结构导致 , 缺页异常不会再次发生 ( 如果再次执行缺失的指令 ) .

对于大于 4KB 的页的分页结构项的 TLB 项 , 软件无法知道使用了多个更小页的转换操作 , INVLPG 指令和缺页会无效所有和转化对应的 TLB 项 .

4.5. Propagation of Paging-Structure Changes to Multiple Processors

修改一个分页结构项的软件可能需要在修改一个分页结构项前 , 先无效源于被修改的分页结构项的 TLB 和分页结构项高速缓存项 . 在多于一个逻辑处理器的系统 , 软件必须考虑除修改分页结构项外的其他逻辑处理器的 TLB 和分页结构高速缓存中也存在对应的项 .

一个分页结构项的改变导致其他处理器也需要无效 TLB 和分页结构项的传播过程 , 称作 “TLB shootdown” .

TLB shootdown 可以通过基于内存的信号量或 / 和处理器间的中断 ( interprocessor interrupts , IPI ) 完成 .

TLB shootdown 必须满足下列条件 :

- 使用被修改的分页结构的所有逻辑处理器必须在修改后执行正确的无效操作 .

- 如果对于分页结构项的修改在 barrier 之前进行 , 或者没有 barrier , 操作系统必须保证以下条件之一成立 :

- 受影响的线性地址范围在修改和无效之间没有被使用 .

- 已经准备好应对修改期间被使用的受影响的线性地址导致的后果 .

- 软件必须准备好处理由于投机执行导致的 , 真实代码路径中不会发生的对于受影响的线性地址空间的读 , 取指 , 预取请求 .

5. Interactions with VMX

VMX transition 可以同时修改 CR0 , CR4 和 IA32_EFER MSR , 因此可以实现在正常情况下无法完成的分页模式转化 .

VMX 提供了 virtual-processor identifiers ( VPIDs ) 和 extended page table ( EPT ) 机制支持地址转换过程 .

VPID 供软件用来向处理器表示不同虚拟处理器的地址空间 , 处理器根据这个信息维护多个地址空间的 TLB 和分页结构高速缓存 .

使用 EPT 时 , 分页结构中的地址作为 guest-physical 地址使用 , 通过一组 EPT 分页结构项生成物理地址 . EPT 还可以指定自己的访问权限和内存类型 .

Author Globs Guo

LastMod 2020-10-13